| Header | Meaning & Role | Driven by / Used by |

|---|---|---|

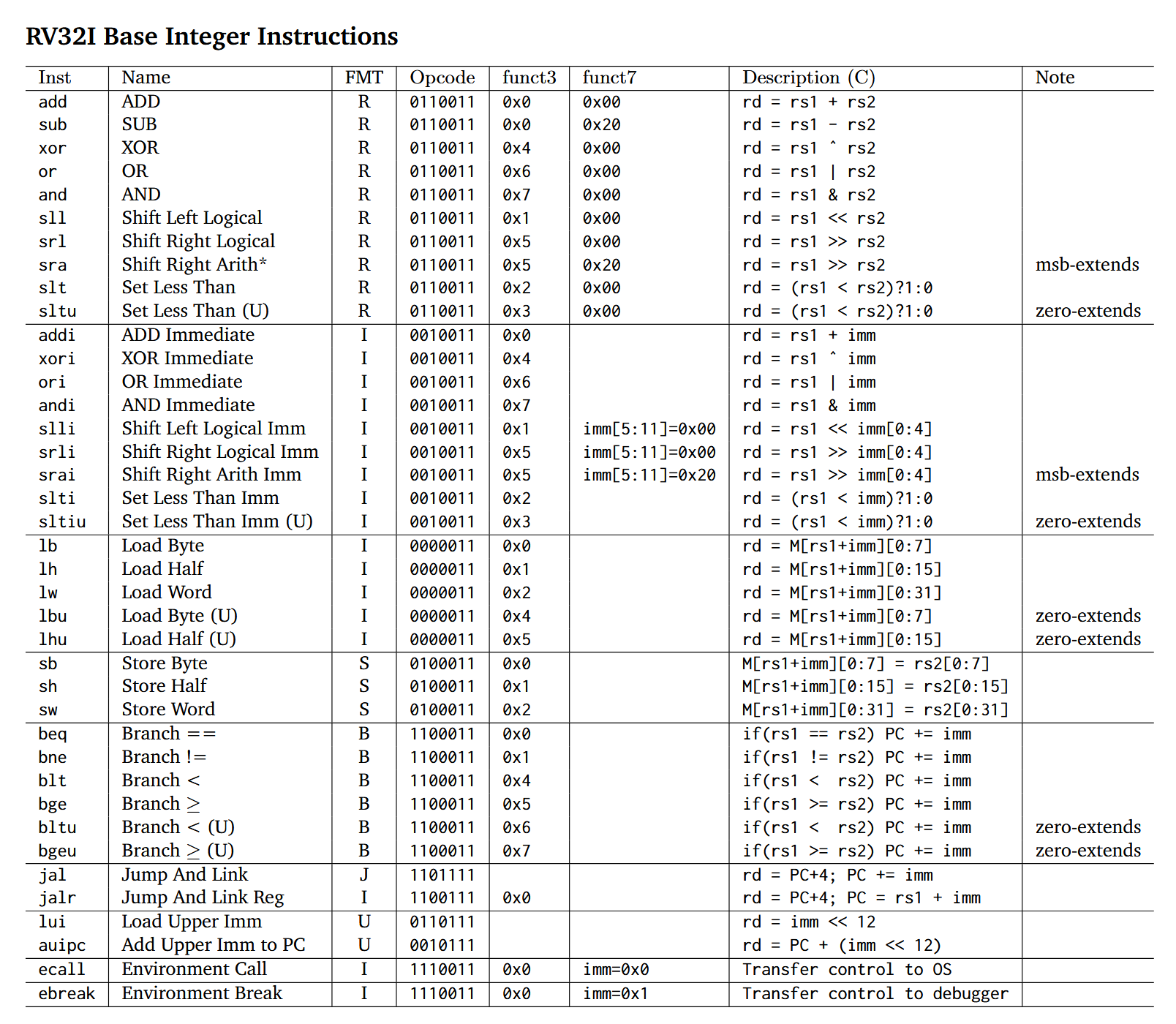

| FMT | Instruction format (R, I, S, B, U, J) — defines how the bits of the instruction are sliced. | Decoding is done by Control Unit, Immediate Generator, and the Instruction Memory provides the raw instruction. |

| Opcode | Bits [6:0] of the instruction, identifies instruction class (e.g., ALU ops, load, branch). | Control Unit receives this; determines instruction type, selects control signals. |

| funct3 | Bits [14:12], sub-function selector within opcode class (e.g., add vs. slt vs. and). | Control Unit uses this for fine control, ALU Control uses this to select exact ALU operation. |

| funct7 | Bits [31:25], sometimes used for further operation decoding (e.g., distinguishing ADD from SUB). | ALU Control examines this along with funct3 for ALU selection; sourced from Instruction Memory. |

| Field | Driven By | Received/Used By |

|---|---|---|

| Opcode | Instruction Memory | Control Unit |

| funct3 | Instruction Memory | Control Unit, ALU Control |

| funct7 | Instruction Memory | ALU Control |

| rs1/rs2/rd | Instruction Memory | RegFile, ALU |

| imm[x:y] | Immediate Generator | ALU, Branch Comparator, etc. |

| PC | PC Unit | Instruction Memory, Adder, Branch Comparator, etc. |

Diagram

---

title: RV32I Instruction Class Diagram

---

classDiagram

note for ArithmeticLogic "R-type & I-type ALU ops"

class ArithmeticLogic {

+add()

+sub()

+xor()

+or()

+and()

+sll()

+srl()

+sra()

+slt()

+sltu()

+addi()

+xori()

+ori()

+andi()

+slli()

+srli()

+srai()

+slti()

+sltiu()

}

note for Load "I-type loads (sign/zero extends)"

class Load {

+lb()

+lh()

+lw()

+lbu()

+lhu()

}

note for Store "S-type stores"

class Store {

+sb()

+sh()

+sw()

}

note for Branch "B-type conditional branches"

class Branch {

+beq()

+bne()

+blt()

+bge()

+bltu()

+bgeu()

}

note for JumpAndLink "J- and I-type jumps"

class JumpAndLink {

+jal()

+jalr()

}

note for UpperImmediate "U-type upper immediates"

class UpperImmediate {

+lui()

+auipc()

}

note for System "I-type system control"

class System {

+ecall()

+ebreak()

}

Quick Example

Instruction: add

FMT:

R— R-typeOpcode:

0110011funct3:

000funct7:

0000000Description:

rd = rs1 + rs2

Components Involved:

Instruction Memory: Provides raw 32-bit instruction.

Control Unit: Decodes opcode, recognizes R-type.

RegFile: Supplies

rs1andrs2data, writes result tord.ALU Control: Looks at funct3 & funct7 to select “add” operation.

ALU: Executes the addition.

See also: